Fehlerprüfung in der Chipproduktion

Ganzheitlicher Ansatz bei der Erkennung und Beseitigung von Fehlern in Chips soll Kosten einsparen.

„Vor zehn, zwanzig Jahren waren die Siliziumchips deutlich einfacher als heute. Seitdem ist die Anzahl ihrer Transistoren in Milliardenhöhe gestiegen. Derartige Chips sind schwierig zu entwerfen, aber noch schwieriger zu testen und zu prüfen. Das Testen und Prüfen ist ganz eindeutig zu einem Engpass im Entwicklungsprozess geworden“, erklärt Jaan Raik, Professor für Prüfung digitaler Systeme am Fachbereich Technische Informatik der Technischen Universität Tallinn in Estland.

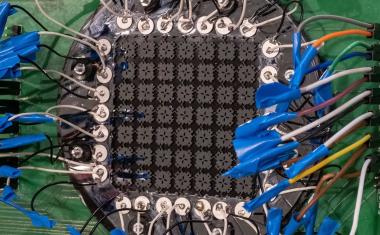

Abb.: Kostensenkung ist eines der Ziele im DIAMOND-Projekt, denn die Fehlersuche ist zum Flaschenhals in der Chip-Produktion geworden. (Bild: DIAMOND)

Das von der EU finanzierte Projekt PROSYD erforschte den Chip-Herstellungsprozess umfassend und stellte dabei fest, dass mehr als 40 Prozent des gesamten IC-Entwicklungszyklus auf die Lokalisierung und Beseitigung von Fehlern im Entwurf aufgewendet werden. In den letzten Jahren wurden zahlreiche Test- und Prüfansätze entwickelt. Obwohl sich damit relativ gut Fehler erkennen lassen, sind sie normalerweise nicht in der Lage, die Ursache eines Fehlers zu bestimmen.

„Es hilft dem Entwickler nicht, wenn er einfach nur weiß, dass der Chip nicht funktioniert. Der Fehler muss lokalisiert und letztendlich auch beseitigt werden. Die letzte Aufgabe wurde bisher relativ wenig berücksichtigt“, erklärt Raik.

Bis jetzt. Für einen Zeitraum von drei Jahren hat sich ein Konsortium aus Universitäten und Technologieunternehmen im Projekt „Diagnosis, error-modelling and correction for reliable systems design“ (DIAMOND) zusammengetan, um innovative Modelle und Technologien zu entwickeln, mit denen sich IC-Fehler testen, erkennen, prüfen und, ganz besonders wichtig, beheben lassen. Mit diesem Ansatz, der mit Finanzmitteln der Europäischen Kommission in Höhe von nahezu 2,9 Mio. EUR unterstützt wurde, macht die Halbleiterindustrie einen enormen Fortschritt – da sich bei weitreichender Einführung riesige Zeit- und Kosteneinsparungen erzielen lassen könnten.

Dem Projektteam zufolge kostet ein modernes Chipentwurfsprojekt etwa 60 Mio. EUR, aber der Prozess für die Fehlererkennung und -beseitigung könnte durch Automatisierung beschleunigt werden, sodass sich die Kosten um 15 Mio. EUR senken ließen. Raik, dem Koordinator von DIAMOND zufolge, konnte mit Hilfe des Projekts ein dreifacher Beitrag zur Lösung des Problems bei der Erkennung und Behebung von IC-Fehlern geleistet werden.

„Erstens wurde ein ganzheitliches Modell für die verschiedenen Fehlerarten entwickelt. Basierend auf diesem Modell können dieselben Lokalisierungsinstrumente für Entwurfsfehler, Soft Error und Defekte verwendet werden. Zweitens wurden automatische Lokalisierungs- und Korrekturverfahren entwickelt. Ein besonderer Schwerpunkt wurde auf Ansätze auf Systemebene gelegt, wo vorherige Forschungsarbeiten nur unzureichende Ergebnisse geliefert hatten. Und drittens wurden Post-Silizium-Ansätze für In-situ-Fehlersuche entwickelt. Derartige Ansätze verlängern die Haltbarkeitsdauer von Siliziumchips, da fehlerhafte Bereiche lokalisiert und isoliert werden können“, sagt er.

Das Team entwarf ein Open Source-System auf Systemebene für die Lokalisierung und Behebung von Entwurfsfehlern mit der Bezeichnung „Formal repair environment for simple C2 (Forensic), das gemeinsam von der Technischen Universität Graz, der Universität Bremen und der Technischen Universität Tallinn entwickelt wurde. Die zweite Version der Umgebung wurde im vergangenen Dezember veröffentlicht.

Um Fehler auf Register Transfer Level zu erkennen und zu beheben, nutzten die Forscher von DIAMOND ein Entwurfsentwicklungssystem namens zamiaCAD. Dabei handelt es sich um eine hoch skalierbare Open Source-Plattform, die problemlos auch große kommerzielle Systeme bewältigen kann, wie sie z. B. die von IBM, einem der industriellen Projektpartner, verwendet werden. Neben dieser Plattform implementierte das Team neue Fehlerlokalisierungsmethoden, mit denen sich Fehler in großen Entwürfen ermitteln lassen.

Da Soft Errors – die beispielsweise durch Strahlung verursacht werden können – in neuen Nanotechnologien verstärkt Probleme bereiten, haben IBM und die Universität Bremen gemeinsam effiziente Simulations- und Anfälligkeitsprüfungen für derartige Fehler entwickelt. In der Zwischenzeit entwickelten Ericsson, die Universität Linköping und das estländische EDA-Unternehmen Testonica ein Post-Silizium-System zum Fehlermanagement, um die Haltbarkeitsdauer künftiger Chips zu verlängern.

Das Ergebnis ist eine deutliche Verbesserung der Effizienz der für die Suche und Behebung von Fehlern verwendeten Prozesse. „Auf Systemebene konnte Forensic 60 Prozent der Benchmark-Entwürfe korrigieren, im Vergleich zu 16 Prozent mit vorherigen Instrumenten“, bemerkt der Projektkoordinator. „Auf Register-Transfer-Level führten wir eine Fallstudie mit einem echten Prozessorentwurf durch. Wir haben mit einem Entwicklungsteam der TU Ilmenau zusammengearbeitet, das uns freundlicherweise dokumentierte Fehler zur Verfügung stellte. Die Methoden des DIAMOND-Projekts ermöglichten die Lokalisierung aller Fehler innerhalb weniger Minuten im Vergleich zu mehreren Stunden bei einer manuellen Suche.“

Aufgrund des Erfolges von DIAMOND bereiten drei der Projektpartner den Start von BASTION, einem Folgeprojekt vor, mit dem die Fehlererkennungstechnologie noch weiter verbessert und das ebenfalls durch die Europäische Kommission finanziell unterstützt werden soll.

EC / PH